DSP TMS320F281x ADC 분석

목차

TMS320F281x ADC 특징

- 두개의 Sample/Hold (S/H) 탑제된 파이프란인 방식(4 Stage)의 12bit ADC

- Simultaneous sampling, Sequential sampling modes 두가지 샘플링 모드 지원

- 입력 허용 전압: 0V ~ 3V

- 샘플/홀드의 신호 획득 시간(S/H acquisition time window) 조절용 클럭 분주 회로 탑재

- 아날로그 먹스가 탑재된 16채널 입력

- 16개의 결과 저장용 버퍼 (ADCRESULT0 ~ 15)

- 두가지 인터럽트 모드 제공

- every end of sequence(EOS) : 신퀀스 동작 매 완료시 마다

- every other EOS : 시퀀스 동작 매 두 번째 완료 시 마다

- 오토 시퀀스 탑재

- 최대 16채널 순서 임의 조정 (cascaded mode : 직렬모드)

- Event Manager A, B와 각각 연계 가능 (dual sequencer mode)

- 연속 동작 모드

- 단일 동작 (Start/Stop) 모드

- Sequencer override mode enhancement

- ADCRESULT 버퍼를 16레벨 FIFO로 사용

- 다양한 트리거 모드 지원 : Start of Conversion (SOC)

- S/W : software immediate start

- EVA : Event manager A (multiple event sources within EVA)

- EVB : Event manager B (multiple event sources within EVB)

- External pin

파이프라인 방식 ADC의 특징

- 각 스테이지의 일괄 (Concurrent) 동작으로 고속 변환 가능

- 고주파 신호에 대한 광범위한 Dynamic Range 제공 가능

- 파이프라인이 꽉 차기 전의 데이터는 의미 없음

- 지연 발생

- 각 스테이지의 ADC 방식은 연속근사방식 (Successive Approximation Register ADC)

ADC 블록 다이어그램

F2810/F2811/F2812

ADC Register 분석

ADCMAXCONV

- Cascaded mode (SEQ1 에서 직렬모드로 사용)

예) SEQ1에서 15채널을 변환한다면 ?

답 = ADCMAXCONV = 0x000E (14), 1을 더한 값 15채널로 설정 된다.

- Dual Sequencer moder

예) SEQ1에 3채널 변환, SEQ2에서 6채널 변환한다면 ?

답 = ADCMAXCONV = 0x0052, 하위 비트(CONV1_x)에 2 설정 1을 더한 값 3채널로 설정 상위 비트(CONV2_x)에 5 설정 1을 더한 값 6채널로 설정 된다.

ADCCHSELSEQ1~4

- 각각 4비트로 구분 채널 지정 : CONVnn

- 채널 변환 순서

- CONV00 > CONV01 > CONV02 > ... CONV15

예) Cascaded 모드로 다음과 같이 순서로 채널을 변환하고자 한다.

ADCINA7 > ADCINA6 > ADCINA0 > ADCINA1 > ADCINA0 > ADCINA2 > ADCINA0 > ADCINA1 > ADCINA0 > ADCINA2

답)

ADCMAXCONV = 0x0009 (10채널)

ADCCHSELSEQ1 = 0x1067 (7, 6, 0, 1)

ADCCHSELSEQ2 = 0x9820 (0, 2, 8=0, 9=1)

ADCCHSELSEQ3 = 0x00A8 (8=0, 10=2)

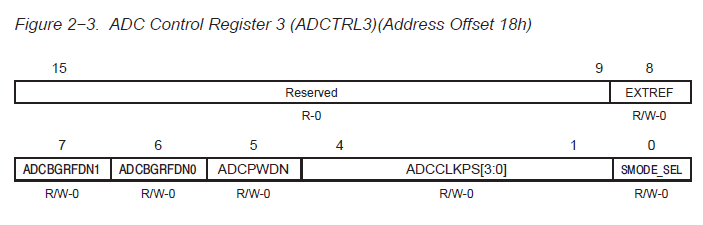

ADCTRL3

- ADCTRL3.8 : EXTREF

- 0 : 내부 레퍼런스 회로 사용

- Power 시퀀스

- ADCBGRFDN[1:0] : Bandgap & Reference Power Down (=0)

파워 레벨에 따른 ADC 운용

- 칩 리셋 후 상태 - ADC Power Down 모드

- ADC를 구동하기

- reference와 bandgap 회로에 전원을 먼저 인가 (ADCBGRFDN[1:0] = 11)

- 최소 7msec 이후에, ADC의 기타 회로에 전원인가 (ADCPWDN = 1)

- 최소 20us 이후에, 첫 변환 시작

- Pipeline 방식의 ADC이기에 초기 몇 샘플은 버릴 것

- 참고: ADCTRL3의 POWER모드 비트에 따른 파워 레벨

ADCST (ADC 상태)

- INT SEQx : SEQx 인터럽트 플래그 비트

- SEQx BSY : SEQx의 동작여부 표시 비트 (1 = in progress)

- INT SEQx CLR : 인터럽트 플래그 클리어 비트

- 1을 쓰면 플래그 클리어

- 언제나 0으로 읽힘

- EOS BUFx

- 인터럽트 모드 0에서는 미사용 비트

- 인터럽트 모드1에서는 매 EOS 마다 토글

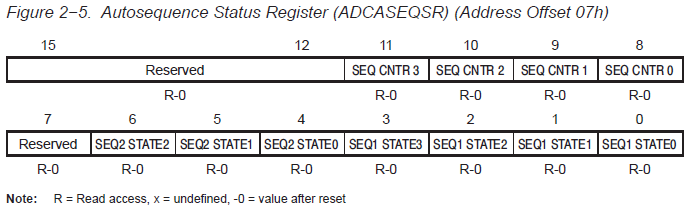

ADCASEQSR (시퀀스 상태)

- 읽기 전용 비트로 구성

- 오토 시퀀스의 상태 표시

- SEQ CNTR3~0

- ADCMAXCONV 레지스터에 정의된 내용을 수행하기 위해 SOC 접수 후, MAX CONV 값이 로딩됨

- SEQx STATEx : TI 내부 테스트용

ADCTRL1

- Reset : ADC 모듈 reset

- 1을 쓰면 리셋, reset 후 이 비트를 읽으면 0 (self cleared)

- ADC 모듈 reset 작업에는 3 사이클 소요 (ADC 관련 레지스터 조작은 reset후 3사이클 뒤에)

- reset 후 ADCTRL1에 값을 대입하기 위해서는 총 12사이클의 NOP등이 필요

- SUMMOD1-0 : 에뮬레이션을 중지했을 때

- 0 0 Mode 0 : 계속해서 동작

- 0 1 Mode 1 : 현재 진행중인 시퀀스 동작 완료 후 정지

- 1 0 Mode 2 : 현재 변환중인 채널을 완료한 후 중지

- 1 1 Mode 3 : 즉시 중지

- ACQ PS3 : 샘플/홀드 시간 설정

- 설정 값 = 비트 + 1

- CPS : ADC 구동 클럭 분주기

- 0 : ADCCLK = HSPCLK/1

- 1 : ADCCLK = HSPCLK/2

- CONT RUN : ADC 의 연속/단일 변환 설정

- 0 : 단일변환 (시퀀스 종료 후에 시퀀스는 정지한다.)

- 1 : 연속변환 (시퀀스 종료 후에 다시 시퀀스를 시작한다.)

- SEQ OVRD

- 0 : Sequencer override 모드 비사용

- 1 : Sequencer override 모드 사용

- SEQ CASC

- 0: Dual sequencer 모드

- SEQ1과 SEQ2를 병렬로 사용하여 1개의 ADC를 2개처럼 사용할 수 있다.

- 단, 각각의 시퀀스는 8채널씩 시퀀스 할 수 있다.

- 1 : Cascaded 모드

- SEQ1과 SEQ2를 직렬로 사용하여 하나의 시퀀스로 사용할 수 있음

- 두 시퀀스를 합쳐 16채널을 시퀀스 할 수 있다.

- 0: Dual sequencer 모드

ADCTRL2

- SOC : 시작하기, Start of Conversion

- Evx SOC : Event Manager로 부터 SOC

- SOC SEQx : 이 비트에 1을 쓰면 SEQ가 동작

- EXT SOC SEQ1 : ADCSOC 핀 입력으로

- EOS : 읽기, End of Conversion

- INT ENA SEQx : ADC 결과를 인터럽트 방식으로 읽음

- INT MOD SEQx : 매 EOS 마다 읽을 것인지, 매 두번째 EOS마다 읽을 것인지 결정

- RST SEQx : 시퀀스를 리셋, CONV00과 CONV08 상태로 초기화

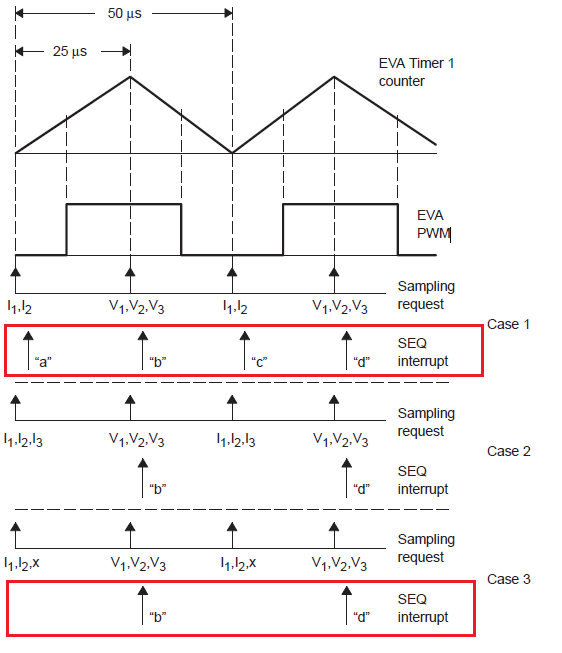

인터럽트 모드

모드 - 1

- 인터럽트 모드 1설정

- MAX CONV = 1로 시작

- I1과 I2 변환

- 인터럽트 서비스 루틴 'a' 에서

- I1, I2 저장

- MAX CONV = 2로 변경

- 인터럽트 서비스 루틴 'b'에서

- V1, V2, V3 저장

- MAX CONV = 1로 변경

- 인터럽트 서비스 루틴 'c, d' 반복

- if, 인터럽트 서비스 루틴 'b'에서 I1, I2, V1, V2, V3 값을 모두 처리한다면, 인터럽트 모드 1은 낭비됨

모드 - 2

- 인터럽트 모드 2 설정

- MAX CONV = 2로 시작

- I1과 I2 변환

- EVA가 Underflow일 때

- I1, I2, x(dummy 채널) 변환

- MAX CONV = 2로 변경

- EVA가 Period Matching일 때

- V1, V2, V3 변환

- 인터럽트 서비스 루틴 'b'에서

- I1, I2, V1, V2, V3 저장

- 다음번 인터럽트 처리 'd'

- dummy 채널 추가로 인터럽트 절제

- 인터럽트 지연 (10Cycle) 제거

ADCRESULTn (12비트 결과 저장)

- ADC 분해능이 증가하면 결과 표현 비트 수가 증가

- 10비트 ADC에 비해 12비트 ADC는 하위 2비트가 증가

- 16비트 레지스터의 최상위 비트부터 채워 나감

- Q number의 자리값

- Q math 이용 시, 자리 이동 필요 없음

샘플링

- 샘플링 주기 : SOC (Start of Conversion)의 주기적 발생

- ADC의 변환 시간과 관계 없음

- 단, Continuous Run Mode 에서는 ADC 자체 변환 시간이 샘플링 주기 결정

예1) 10KHz로 샘플링

답 = Event Manager의 주기 이벤트를 이용해서 10KHz 주기로 SOC 발생

예2) ADCTRL1.6의 CONT_RUN 비트 설정

답 = ADC 변환 시간(시퀀스 한 세트) : 샘플링 주기

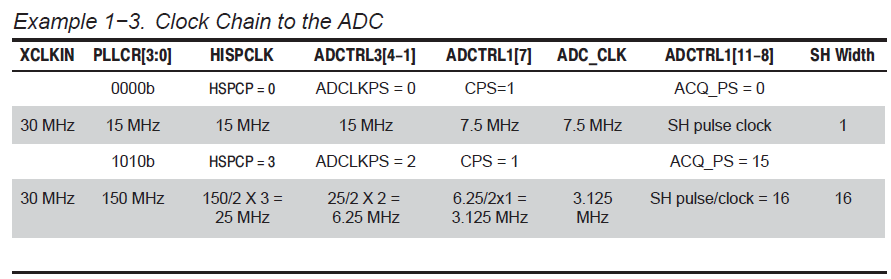

변환 시간(속도)

- ADC 모듈이 S/H에 샘플링된 아날로그 신호를 디지털 신호(PCM 데이터)로 변환하는 시간

- ADC 회로 구동 클럭이 변환 시간 결정

변환 속도 계산

- 변환 속도가 7.5MHz로 설정되었다 하더라도, SOC의 발생 주기가 10KHz이면 샘플링 주기(rate)는 10KHz 이다.

ADC 구동 클럭을 높이면

- Aliasing이 줄어든다.

- 채널간 오차(cross-talk)가 커진다.

- 이 오차는 샘플링 윈도우를 키운다고 줄어드는 성질의 것이 아니다.

ADC 구동 클럭을 낮추면

- Aperture Error가 커진다.

주의 1: 구동 클럭과 샘플링 rate은 별개

- 1KHz로 샘플링을 하더라도, ADC 구동 클럭은 25MHz가 가능하다.

주의 2: 281x ADC의 최고 구동 클럭은 25MHz

- 분주 부주의로 25MHz이상의 클러이 공급되면, 결과가 맞지않다.

시퀀스

- 채널 변환 순차 설정이 주된 동작

- 개발자가 시퀀스에 기동 신호를 전달하면, 시퀀스가 ADC 회로를 기동

- 시퀀스 설정 완료 인터럽트 발생 가능

- 다채널 조작 용이

8채널 조작 시퀀스 2개 탑재

- SEQ1: ADCINA0~7 > S/H-A

- SEQ2: ADCINB0~7 > S/H-B

- 16채널 조작 단일 시퀀스로 운용 가능(Cascaded 모드)

시퀀스의 장점

- Multi-rate System 구현 용이

- 고속 샘플링 지원 용이

- 12.5MHz 샘플링 : 샘플링당 12개의 명령어 처리

- 블록 샘플링 :

- 최고 16회 혹은 16채널 변환을 1블록으로

- 시퀀서 완료 주기는 약 780KHz(12.5MHz/16)

- 인터럽트 처리 가능

- 주변 회로 연계 구동 능력

- 초기 설정만으로 ADC 구동 가능

- 타이머 주기 이벤트를 이용한 ADC 기동

- 유연한 ADC 기동과 결과 처리 가능

- 초기 설정만으로 ADC 구동 가능

시퀀스 : Cascaded(직렬) 모드

시퀀스 : Dual Sequencers(병렬) 모드

DSP281x_Adc.c 의 전원 관련 코드

//---------------------------------------------------------------------------

// InitAdc:

//---------------------------------------------------------------------------

// This function initializes ADC to a known state.

//

void InitAdc(void)

{

extern void DSP28x_usDelay(Uint32 Count);

// To powerup the ADC the ADCENCLK bit should be set first to enable

// clocks, followed by powering up the bandgap and reference circuitry.

// After a 5ms delay the rest of the ADC can be powered up. After ADC

// powerup, another 20us delay is required before performing the first

// ADC conversion. Please note that for the delay function below to

// operate correctly the CPU_CLOCK_SPEED define statement in the

// DSP28_Examples.h file must contain the correct CPU clock period in

// nanoseconds. For example:

AdcRegs.ADCTRL3.bit.ADCBGRFDN = 0x3; // Power up bandgap/reference circuitry

DELAY_US(ADC_usDELAY); // Delay before powering up rest of ADC

AdcRegs.ADCTRL3.bit.ADCPWDN = 1; // Power up rest of ADC

DELAY_US(ADC_usDELAY2); // Delay after powering up ADC

}